# BIRZEIT UNIVERSITY

ENCS2110

# DIGITAL ELECTRONICS AND COMPUTER ORGANIZATION LABORATORY Experiment 5: Sequential Logic Circuits

Name: Sara Totah

Student ID: 1181779

Instructor: Khader Mohammed T.A: Enas Jawabreh

Date: 20/03/2021

# Table of Contents

| Table of  | Figures                                                | . 2 |

|-----------|--------------------------------------------------------|-----|

| Abstract  |                                                        | . 3 |

| Pre-Lab.  |                                                        | . 3 |

| The SI    | R (set-Reset) Latch                                    | .3  |

| RS La     | tch with Control input                                 | . 3 |

| D-Late    | ch                                                     | .4  |

| Theory    |                                                        | . 5 |

| Seque     | ntial Circuits                                         | . 5 |

| Latche    | 28                                                     | .5  |

| 1.        | The SR (Set-Reset) Latch                               | . 5 |

| 2.        | The D Latch                                            | .6  |

| Flip-F    | lops                                                   | .6  |

| 1.        | D Flip flop                                            | .6  |

| 2.        | JK Flip flop                                           | .7  |

| 3.        | T flip flop                                            | .7  |

| Regist    | ers                                                    | .7  |

| Shif      | ft register                                            | .7  |

| Count     | ers                                                    | . 8 |

| 1.        | Ripple Counters (Asynchronous)                         | . 8 |

| 2.        | Synchronous Counters                                   | . 8 |

| The proc  | edure, Data and Results                                | .9  |

| Latche    | es and Flip flops                                      | .9  |

| А.        | Constructing RS latch with Basic Logic Gates           | .9  |

| В.        | Constructing an RS latch with control input            | .9  |

| C.        | Constructing D latch with RS latch                     | 10  |

| D.        | Constructing JK latch with RS latch                    | 11  |

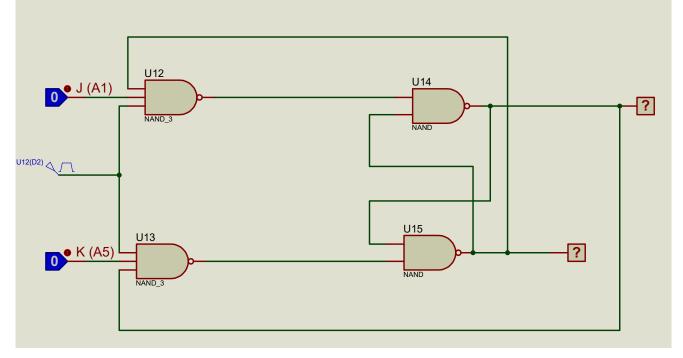

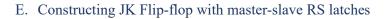

| E.        | Constructing JK Flip-flop with master-slave RS latches | 11  |

| Regist    | ers                                                    | 12  |

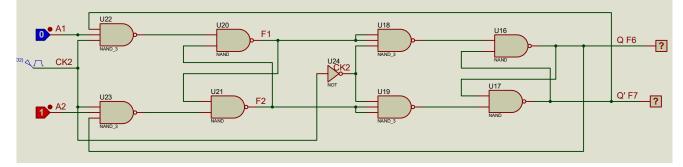

| А.        | Constructing Shift Register with D Flip-Flops          | 12  |

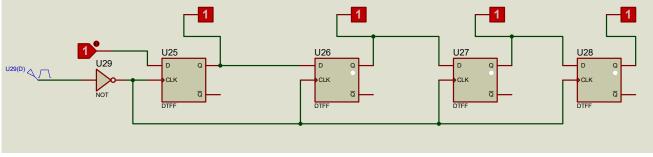

| В.        | 4-Bit Shift Register with serial and parallel load     | 12  |

| Count     | ers                                                    | 13  |

| А.        | 2-bit Synchronous Counter                              | 13  |

| В.        | 3-bit (divide-by-eight) Ripple Counter                 | 14  |

| C.        | BCD Counter                                            | 14  |

| Post-Lab  | ,                                                      | 15  |

| Task 1    | l                                                      | 15  |

| Task 2    | 2                                                      | 15  |

| Discussio | ən                                                     | 16  |

| Conclusi  | on                                                     | 16  |

| Referenc  | es                                                     | 17  |

# Table of Figures

| Figure 1: SR Latch with NAND gate                              | 3  |

|----------------------------------------------------------------|----|

| Figure 2: RS Latch with control input                          | 3  |

| Figure 3: D-Latch                                              | 4  |

| Figure 4: D flip flop with two D latches                       | 4  |

| Figure 5: Sequential Circuits                                  | 5  |

| Figure 6: RS latch with NAND gates and RS latch with NOR gates | 5  |

| Figure 7: D Latch                                              | 6  |

| Figure 8: D Flip flop with two D latches                       | 6  |

| Figure 9: D flip flop symbol                                   | 7  |

| Figure 10: JK flip flop symbol                                 | 7  |

| Figure 11: T flip flop symbol                                  | 7  |

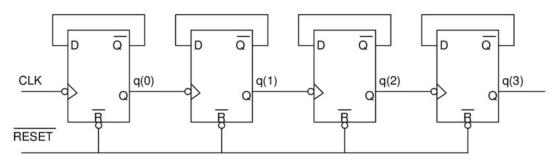

| Figure 12:4-bit shift-right register                           | 7  |

| Figure 13:4-bit ripple counter                                 | 8  |

| Figure 14: Synchronous Counter                                 | 8  |

| Figure 15: RS latch                                            | 9  |

| Figure 16: RS Latch with control input                         | 9  |

| Figure 17: D Latch                                             | 10 |

| Figure 18: JK Latch                                            | 11 |

| Figure 19: JK Flip-Flop                                        | 11 |

| Figure 20: Shift Right Register                                | 12 |

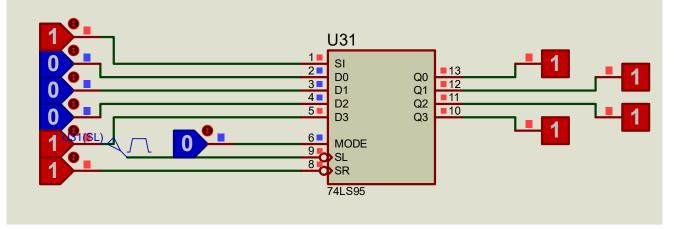

| Figure 21: Shift register with serial and parallel load        | 12 |

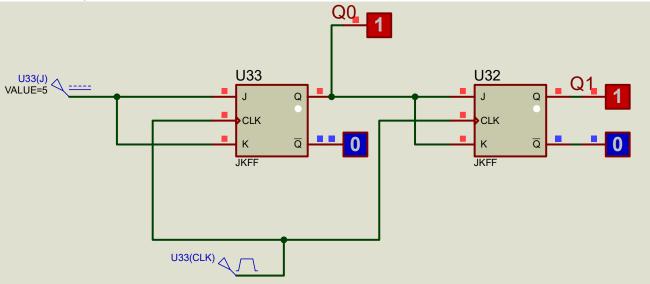

| Figure 22: 2-bit Synchronous Counter                           | 13 |

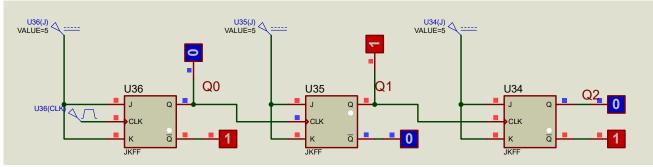

| Figure 23: 3-bit Ripple Counter                                | 14 |

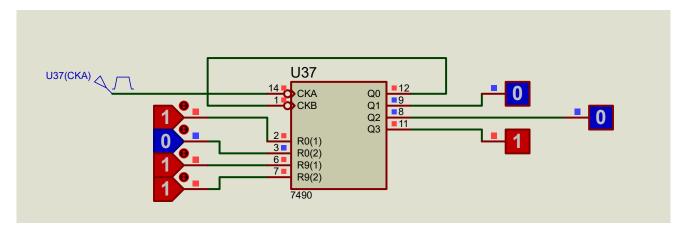

| Figure 24: IC 7490 BCD Counter                                 | 14 |

| Figure 25: 3-bit Synchronous Counter                           | 15 |

| Figure 26: 0-5 Counter                                         | 15 |

| Figure 27: 0-4 Counter                                         | 15 |

# Abstract

This experiment aims to understand the difference between the sequential and combinational logic circuit in addition to understanding how to flip flops to work (D flip-flop & JK flip-flop).

#### Equipment used:

We were supposed to use a Basic Electricity Circuit Lab, JK Flip-flop circuits and Flip-flop circuits, but since the experiment was implemented online due to the pandemic, we used proteus software.

## Pre-Lab

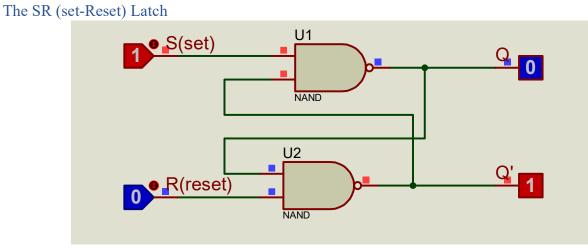

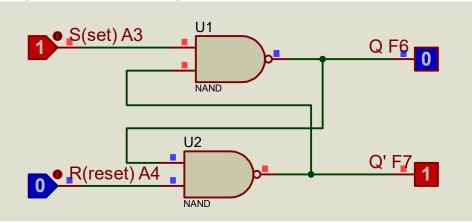

Figure 1: SR Latch with NAND gate

| S | R | Q | Q' |                    |

|---|---|---|----|--------------------|

| 1 | 0 | 0 | 1  |                    |

| 1 | 1 | 0 | 1  | After S = 1, R = 0 |

| 0 | 1 | 1 | 0  |                    |

| 1 | 1 | 1 | 0  | After S = 0, R = 1 |

| 0 | 0 | 1 | 1  |                    |

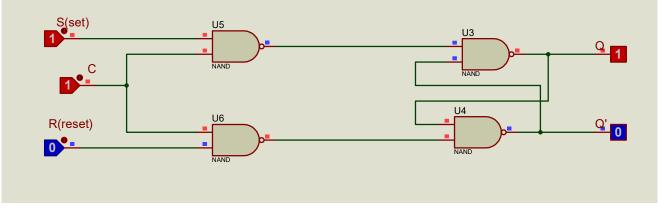

#### RS Latch with Control input

Figure 2: RS Latch with control input

| С | S | R | NEXT STATE OF Q   |

|---|---|---|-------------------|

| 0 | Х | Х | No change         |

| 1 | 0 | 0 | No change         |

| 1 | 0 | 1 | Q = 0 Reset state |

| 1 | 1 | 0 | Q= 1 set state    |

| 1 | 1 | 1 | Indeterminate     |

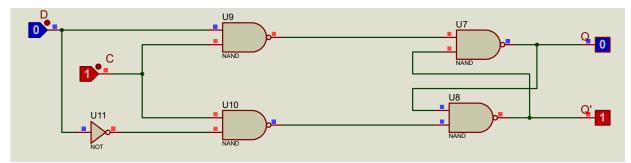

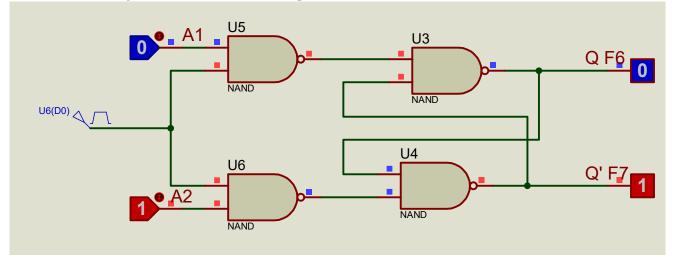

# D-Latch

Figure 3: D-Latch

| С | D | Next state of Q   |

|---|---|-------------------|

| 0 | Х | No Change         |

| 1 | 0 | Q = 0 Reset state |

| 1 | 1 | Q = 1 Set state   |

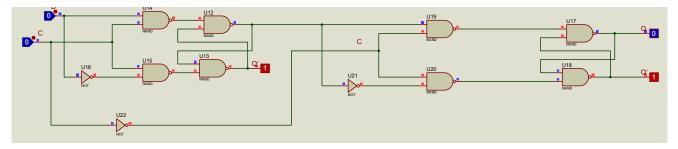

Figure 4: D flip flop with two D latches

# Theory

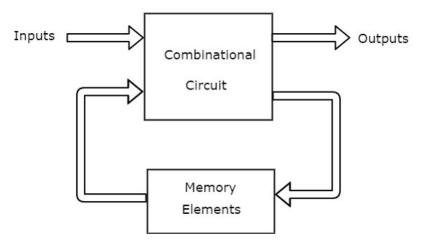

#### Sequential Circuits

A sequential circuit has a memory so output can vary depending on the input and previous output which was saved in the memory.

Figure 5: Sequential Circuits

There are two types of memory elements depending on the type of triggering that is suitable to operate

#### Latches

Latches are basic storage elements that are level-sensitive devices, they are controlled by a clock, there are a couple of types for the latches, which are:

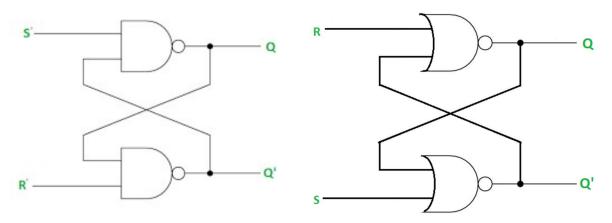

#### 1. The SR (Set-Reset) Latch

This latch needs two inputs (Set and Reset) and two outputs, it can be implemented using 2-cross-coupled NOR gates or two cross-coupled NAND gates.

Figure 6: RS latch with NAND gates and RS latch with NOR gates

| Q | Q' | STATE |

|---|----|-------|

| 1 | 0  | Set   |

| 0 | 1  | Reset |

| S | R | Q | Q' |   |

|---|---|---|----|---|

| 1 | 0 | 0 | 1  |   |

| 1 | 1 | 0 | 1  | A |

| 0 | 1 | 1 | 0  |   |

| 1 | 1 | 1 | 0  | A |

| 0 | 0 | 1 | 1  |   |

After S = 1, R = 0

After S = 0, R = 1

Indeterminate

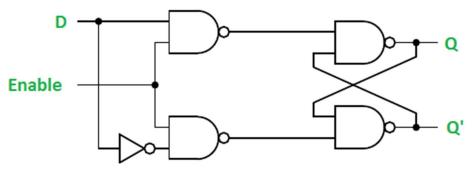

#### 2. The D Latch

The input in this type is more complicated than the ones in SR latches

Figure 7: D Latch

It was developed to eliminate the undefined condition of the indeterminate in the RS latch

| С | D | Next state of Q   |

|---|---|-------------------|

| 0 | Х | No Change         |

| 1 | 0 | Q = 0 Reset state |

| 1 | 1 | Q = 1 Set state   |

#### **Flip-Flops**

This also is a sequential circuit, it's a 1-bit memory cell that can be used to store digital data, and can be said that the flip flop is an edge-triggered device, it also has some types:

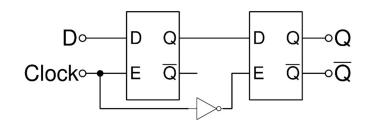

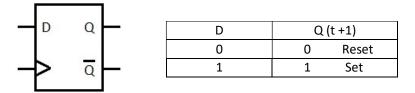

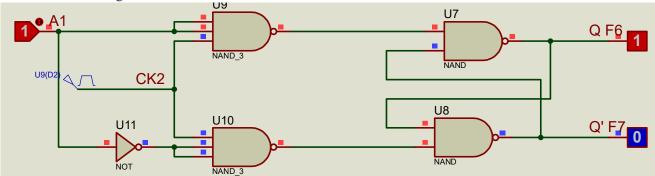

#### 1. D Flip flop

Figure 8: D Flip flop with two D latches

Figure 9: D flip flop symbol

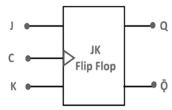

2. JK Flip flop

| J | K | Q (t +1)<br>Q(t) No change |       |

|---|---|----------------------------|-------|

| 0 | 0 |                            |       |

| 0 | 1 | 0                          | Reset |

| 1 | 0 | 1                          | Set   |

| 1 | 1 | Q'(t) Complement           |       |

Figure 10: JK flip flop symbol

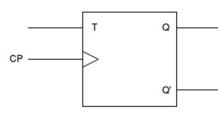

3. T flip flop

| - | Т | Q (t +1)         |  |

|---|---|------------------|--|

|   | 0 | Q(t) No Change   |  |

|   | 1 | Q'(t) Complement |  |

Figure 11: T flip flop symbol

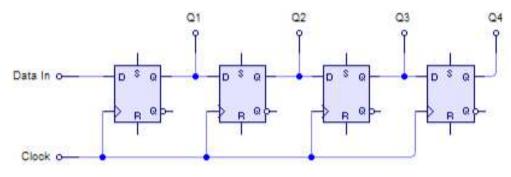

#### Registers

As it was mention before the flip-flop is a 1bit memory cell, to increase the storage capacity (number of bits), we can use several flip-flops, and this group is called **Register**, N flip-flops together make an N-bit register, all the flip-flops are driven by the same clock, as an example of the registers is the shift-right register.

Figure 12:4-bit shift-right register

#### Shift register

Group of flip-flops connected so that the output of the first flip-flop is the input for the second one and so on.

#### Counters

The counter is a special type register that goes through a prescribed sequence of states, there are two types of counters: Ripples and synchronous

#### 1. Ripple Counters (Asynchronous)

It's an asynchronous counter, it counts up to  $2^n$  states, it is known by that name due to the way the clock pulse ripples its way through the flip-flops.

Figure 13:4-bit ripple counter

2. Synchronous Counters (Logic 1) 8 FFA FFB FFC FFD Out QB QA Qc QD J J J J Qc QA CLK CLK QB CLK CLK QD QD Q\_A QB К Qc κ К κ 0 Clock Pulse

# The procedure, Data and Results

#### Latches and Flip flops

A. Constructing RS latch with Basic Logic Gates

#### Figure 15: RS latch

| A3 | A4 | F6 | F7 |

|----|----|----|----|

| 0  | 0  | 1  | 1  |

| 0  | 1  | 1  | 0  |

| 1  | 0  | 0  | 1  |

| 1  | 1  | 0  | 1  |

We noticed that when A3 and A4 were set to equal zero, both Q and Q' became 1 which is not allowed, so this case is prohibited, if A3 = 0 and A4 = 1, then Q would equal 1 and be at the SET state when reversing both inputs (A3 = 1, A4 = 0) Q will be 0 (at the RESET state), if both inputs were set to equal 1, no change will happen to the output it will remain the same as before.

#### B. Constructing an RS latch with control input

Figure 16: RS Latch with control input

| Al | A2 | F6        | F7        |

|----|----|-----------|-----------|

| 0  | 0  | No change | No change |

| 0  | 1  | 0         | 1         |

| 1  | 0  | 1         | 0         |

| 1  | 1  | 1         | 1         |

If A1 = 0 and A2 = 1 then the output Q would equal 0 and Q' = 1, if we changed A2 to zero the outputs won't change, and we noticed too that the case when both inputs = 1 is a prohibited case since both Q and its complement = 1 which is not allowed.

C. Constructing D latch with RS latch

Figure 17: D Latch

| CK2 | A1 | F6     |

|-----|----|--------|

| 0   | 0  | memory |

| 0   | 1  | memory |

| Л   | 0  | 0      |

| Л   | 1  | 1      |

First, if we set the clock to zero, there will be no output no matter what the input A1 was, but after changing the clock into 1 and setting the input to 0 the output will equal zero, and after setting the input A1 to 1 the output will equal one, after any case of the last two cases, if we changed the clock back to zero the output will keep holding the result it already got from the last time.

Figure 18: JK Latch

| СК | A1 | A5 | F6         |

|----|----|----|------------|

| Л  | 0  | 0  | memory     |

| Л  | 0  | 1  | 0 Reset    |

| Л  | 1  | 0  | 1 Set      |

| Л  | 1  | 1  | Complement |

The JK flip-flop is an SR flip-flop with feedback if both inputs (A1 & A5) are set at logic 0 (J = K = 0), no matter what the clock state was the flip-flop will keep containing the data it already has (as a memory), but when both inputs are set to 1 (J = K = 1) the output will switch and change his state to its complement for example if the J = 1 and K = 0 the output state will be SET the output F6 = 0, so when changing the K value to 1 the output will be the complement of the previous output.

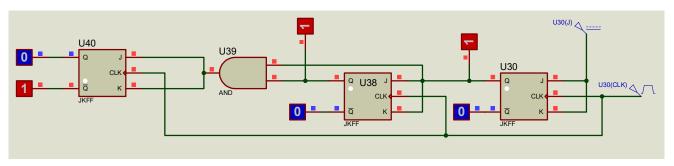

Figure 19: JK Flip-Flop

| СК | K | J | F1 | F2 | F6 | F7 |

|----|---|---|----|----|----|----|

| Л  | 0 | 0 | 1  | 0  | 1  | 0  |

| Л  | 0 | 1 | 0  | 1  | 1  | 0  |

| Л  | 1 | 0 | 1  | 0  | 0  | 1  |

| Л  | 1 | 1 | 0  | 1  | 1  | 0  |

| Л  | 1 | 1 | 1  | 0  | 0  | 1  |

### Registers

A. Constructing Shift Register with D Flip-Flops

Figure 20: Shift Right Register

When we set the input to equal 1, on each clock pulse the register shifts the input which equals 1, in this case, 1-bit to the right.

#### B. 4-Bit Shift Register with serial and parallel load

Figure 21: Shift register with serial and parallel load

| MODE | SL | Q3 | Q2 | Q1 | Q0 |

|------|----|----|----|----|----|

| 0    | Л  | 1  | 0  | 0  | 1  |

| 0    | Л  | 0  | 0  | 1  | 1  |

| 0    | Л  | 0  | 1  | 1  | 0  |

| 1    | Л  | 1  | 1  | 0  | 0  |

#### Counters

#### A. 2-bit Synchronous Counter

Figure 22: 2-bit Synchronous Counter

| CLK | Q1 | Q0 |

|-----|----|----|

| Л   | 0  | 0  |

| Л   | 0  | 1  |

| Л   | 1  | 0  |

| Л   | 1  | 1  |

| Л   | 0  | 0  |

| Л   | 0  | 1  |

| Л   | 1  | 0  |

| Л   | 1  | 1  |

First, both Q2 and Q1 were in the reset state, after the second clock edge, Q0 should change from 0 to 1, but both J1 and K1 = 0 so the second flip-flop won't change its state so Q1 will stay 0.

After the third clock edge, Q0 changes from 1 to 0 again, but J2 and K2 now = 1 so Q1 changes from 0 to 1

After the fourth clock edge, Q0 will change to 1 but the Q1 will remain the same.

After the fifth clock edge, Q0 will change to 0 and Q1 will change to 0 too, now they are back to the reset state.

#### B. 3-bit (divide-by-eight) Ripple Counter

Figure 23: 3-bit Ripple Counter

| CLK | Q2 | Q1 | Q0 |

|-----|----|----|----|

| Л   | 0  | 0  | 0  |

| Л   | 0  | 0  | 1  |

| Л   | 0  | 1  | 0  |

| Л   | 0  | 1  | 1  |

| Л   | 1  | 0  | 0  |

| Л   | 1  | 0  | 1  |

| Л   | 1  | 1  | 0  |

| Л   | 1  | 1  | 1  |

Here there are three flip-flops so the counter can count up to  $2^3 = 8$  values.

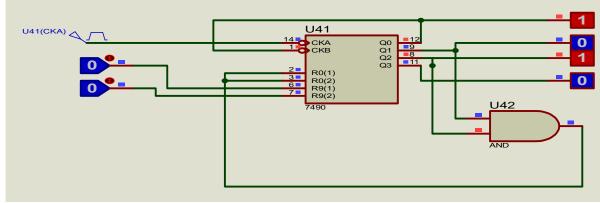

#### C. BCD Counter

Figure 24: IC 7490 BCD Counter

# Post-Lab

#### Task 1

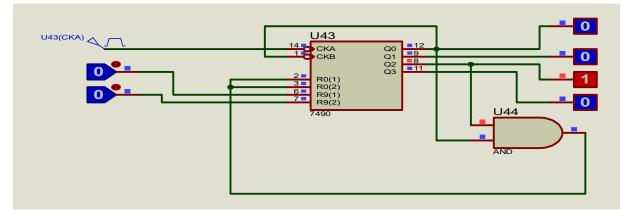

Modify the circuit in Figure 22 to be a 3-bit Synchronous Counter. Attach the design with this experiment report.

Figure 25: 3-bit Synchronous Counter

#### Task 2

Change the connection of counter in Figure 24 to count from:

- 0-to-5

Figure 26: 0-5 Counter

#### - 0-to4

Figure 27: 0-4 Counter

## Discussion

# Although latches are useful for storing binary information, they are rarely used in sequential circuit design, why?

It's right that the latches are faster than the flip-flops since the flip-flops consist of several latches, and they consume less power but the latches tend to make glitches which are not appreciated in the designing, also the latches are level triggered as mentioned before while the flip-flops are edge-triggered, so the change in the flip-flop will happen only at the triggering edge.

#### What is the disadvantage of the RS flip flops?

The major disadvantage is when both inputs are 1 (S=R=1) in this case the output and its complement will be 1 which is not allowed.

#### What is the difference between "synchronous" and "ripple" counters?

At the ripple-counters, each flip-flop is triggered with its clock, while at the synchronous counter all flipflops are triggered with the same clock so the synchronous counter should be faster than the ripple counter.

### Conclusion

In this experiment the meaning of sequential circuits and the concept of memory units such as latches and flip-flop was covered, the experiment went smoothly with no troubles.

# References

- <u>https://www.tutorialspoint.com/computer\_logical\_organization/sequential\_circuits.htm</u>

- https://www.geeksforgeeks.org/latches-in-digital-logic/

- <u>https://www.tutorialspoint.com/digital\_circuits/digital\_circuits\_latches.htm</u>

- <u>https://www.tutorialspoint.com/computer\_logical\_organization/digital\_counters.htm</u>

- Digital Lab manual.